IC<sup>TM</sup> Value: 3.00

# INTERNATIONAL JOURNAL OF ENGINEERING SCIENCES & RESEARCH TECHNOLOGY

ISSN: 2277-9655

**Impact Factor: 4.116**

## DESIGN OF LOW-POWER FULL ADDER IN 0.18 $\mu m$ CMOS TECHNOLOGY Rohit Kumar $^*$ , Sachin Tyagi

\*Assistant Engineer, Uttarakhand Council for Biotechnology, Biotech Bhawan, Haldi-263146, Pantnagar, U. S. Nagar, Uttarakhand, India

Assistant Professor, Electronics & Communication Engineering, Roorkee College of Engineering, Roorkee, India

**DOI**: 10.5281/zenodo.59758

#### **ABSTRACT**

With the increase in device integration level and the growth in complexity of Integrated circuits, small delay and low power dissipation become important parameters as these increases performance and portability. Battery storage is limited, to extend battery life; low power operation is the primary requirement in integrated circuits. Furthermore, high speed and multiple parallel applications need high computing power, placing greater demands on energy storage elements within the system. Large power dissipation in high performance digital systems requires large size heat sinks. These off chip component makes chip bulky and require large space. Secondly, extra heat in integrated circuit degrades the system performance. The full adder (FA) is a very important and basic building block in Arithmetic and Logic unit (ALU) of digital processor. The most widely accepted metrics to measure the quality of a digital circuit or to compare various circuit styles is power delay product. Further, Portability imposes a strict limitation on power dissipation while needs more computational speeds. The reduced power consumption and the improved speed require optimizations at all levels of the design procedure.

CMOS technology has low power dissipation. Many researchers have developed various logic styles to implement Full Adder such as conventional static CMOS, dynamic CMOS, transmission gates, NORA[38] which has various advantages and limitation. Conventional Static CMOS has been used in much processor design. Static Pass Transistor circuit can also be used for Low Power applications. Dynamic circuit is also useful in Low Power high speed systems with careful clocking. Reversible logic is also noticeable recently for reducing the power dissipation. Quantum arithmetic component design requires reversible logic circuits. Reversible logic circuits has several applications such as in low power digital design, nanotechnology, DNA and quantum computing.

In the proposed work, the limitation associated with the above mentioned design style are studied and the transistor count reduction is done to reduce the power dissipation. The newly proposed structures will be simulated using SYMICA simulator software and  $0.18~\mu m$  CMOS technology is selected for simulation. The proposed design will definitely reduce the power dissipation at-least 20%.

KEYWORDS: Power reduction, CMOS, GDI, PTL, symica simulator.

## **INTRODUCTION**

In the past years, the VLSI designers targeted the performance and miniaturization mainly. High power consumption is an alarming issue with the substantial growth in portable electronics devices. There are problems with heat removal and cooling of the device as the power dissipation per unit area increases with scaling. The portable battery-operated electronic devices were initially known by low computational requirement. But, recently there is a need of high computational performance by the applications. It is therefore important to extend the battery life. With these reasons power dissipation is very important issue for circuit designers[44].

[Kumar\**et al.*, 5(8): August, 2016] IC<sup>TM</sup> Value: 3.00

Static power dissipation from standby leakage currents is an critical parameter of total power dissipation. Electronic devices have different types of component and some of them may remain inoperative during a specific operation. Large percentage of total power dissipation in the system is due to the static power dissipation in these inoperative components. The performance of MOS devices is remarkable enhanced due to the continued scaling of MOS devices,. This infact increased the power dissipation due to leakage currents. Now, this leakage component becomes an important parameter for power efficient system. Also, there is continuous evolution of low power and low voltage CMOS VLSI circuits day-by-day.

#### **Full Adder**

A full adder is a combinational circuit that forms the arithmetic sum of three input bits. Beside three inputs, it has two outputs two of the input variables denoted by A and B, represent the two significant bits to be added. The third input, C<sub>in</sub>, represents the carry from the lower significant position. Two outputs are necessary because the arithmetic sum of three bits ranges in value from 0 to 3 and binary 2 and 3 need two digits for their representation again, the two outputs are designated by the symbol 'S' for SUM and 'Cout' for carry output. The simplified sum-of-product functions for the two outputs are

$$S = \bar{A}.\bar{B}.C_{in} + \bar{A}.B.\bar{C}_{in} + A.\bar{B}.\bar{C}_{in} + A.B.C$$

(1)

ISSN: 2277-9655

**Impact Factor: 4.116**

$$C_{out} = A.B + B.C_{in} + C_{in}.A$$

(2)

## MATERIALS AND METHODS

## PREVIOUS WORK

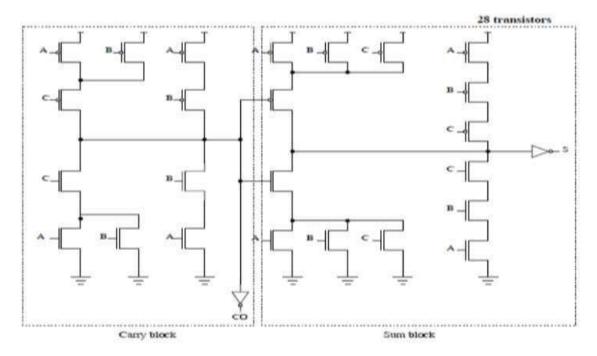

## A. 28T CMOS FULL ADDER:

This adder is based on CMOS structure (pull-up and pull-down network).

Fig. 1.Conventional 28-T CMOS full adder[19].

C<sub>out</sub> is generated first then the sum is derived. One of the most significant advantages is the higher noise margins and in turn reliable low voltage operation. The larger number of transistors results in increased input loads, higher power consumption and more silicon area[19].

ISSN: 2277-9655 ICTM Value: 3.00 **Impact Factor: 4.116**

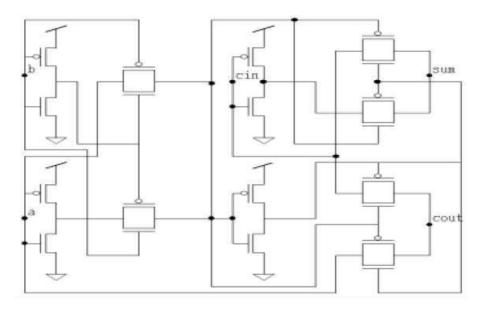

## **B. 20 T TRANSMISSION GATE FULL ADDER:**

It produces buffered outputs with proper polarity with the disadvantage of high power consumption.

Fig. 2.-T transmission Gate Full Adder[19][28].

In this design 2 inverters with two transmission gates are used which act as 8-T XOR and 8-T XNOR module. To generate Sum; Cin and Cin' are multiplexed controlled either by (a 4b) or (a 4b)'. Similarly the Cout is the multiplexed output of A and Cin controlled by (a.b). This is one of the fastest adder so far. This circuit is simple but the power dissipation in this circuit is more than the 28T adder. But with same power consumption it performs faster [19][28].

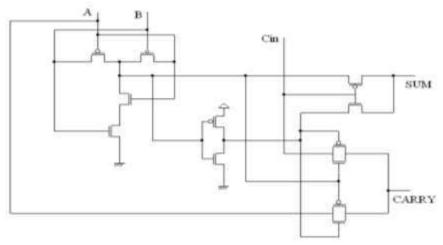

## **C.14T FULL ADDER:**

The 14T full adder has a 4 transistor PTL XOR gate, shown in Fig. 31, an inverter and two transmission gates for generating sum and Cout signals[19][31].

Fig. 3- T Full Adder[19][31]

ICTM Value: 3.00

ISSN: 2277-9655 **Impact Factor: 4.116**

This circuit has a four transistor XOR which is inverted to generate XNOR. These XOR and XNOR are used to obtain SUM and Cout. The Cout is generated by multiplexing A and Cin controlled by (a.b). This is one of the fastest adder and simpler than the conventional adder. In comparision with 28T adder the power dissipation in this circuit is higher. However with same power consumption it performs faster [24].

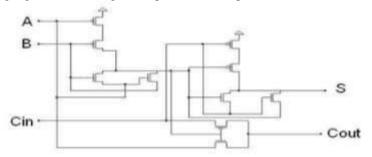

#### D.10T STATIC ENERGY RECOVERY FULL ADDER:

The energy recovering logic reuses charge and power consumption is less than non-energy recovering logic.

Fig. 4-T SERF Full Adder[19][32].

The circuit consists of two XNORs realized by 4 transistors. Sum is generated from the output of the second stage XNOR circuit. The cout can be calculated by multiplexing A and Cin controlled by (A XOR B).Let us consider that there is a capacitor at the output node of the first XNOR module. To illustrate static energy recovery let us consider an example where initially A=B=0and then a changes to 1. When a and b both equals to zero the capacitor is charged by VDD. In the next stage when breaches a high voltage level keeping a fixed at a low voltage level, the capacitor discharges through a. Some charge is retained in a. Hence when a reaches a high voltage level we do not have to charge it fully. So the energy consumption is low here. It should be noted that the new SERF adder has no direct path to the ground. The elimination of a path to the ground reduces power consumption. The charge stored at the load capacitance is reapplied to the control gates. The combination of not having a direct path to ground and the re-application of the load charge to the control gate makes the energy-recovering full adder an energy efficient design. The circuit produces full-swing at the output nodes. But it fails to provide so for the internal nodes. As the power consumption by the circuit reduces the circuit becomes slower. Also it cannot be cascaded at low power supply due to multiple threshold problems[19][32].

## E. 10T FULL ADDERS REALIZED BY GATE DIFFUSION INPUT (GDI) STRUCTURES:

Now using these GDI based XOR and XNOR gates two different GDI based full adder architecture were designed [Fig. 19].

Fig. 5.(a)GDI XOR Adder[19][26] Fig. 5.(b) GDI XNOR Adder [19][26].

ICTM Value: 3.00

ISSN: 2277-9655 Impact Factor: 4.116

The circuit operation of GDI Based Full Adders is exactly the same as that of previous SERF module. Sum bit is obtained from the output of the second stage of XOR [Fig. 33(a)], XNOR[Fig. 33(b)] circuit while Carry bit (Cout) is calculated by multiplexing B and Cin controlled by (A XNOR B). These features give the GDI cell two extra input pins to use which makes it flexible than usual CMOS design. It is also a genius design which is very power efficient without huge amount of transistor count. The major problem of a GDI cell is that it requires twin-well CMOS or silicon on insulator (SOI) process to realize. Thus, it will be more expensive to realize a GDI chip. Moreover if only standard p-well CMOS process is used, the GDI scheme will face the problem of lacking driving capability which makes it more expensive and difficult to realize as a feasible chip[19][26].

## F. ADDER 9A AND 9B:

Fig. 6. (a) Adder 9A[19][33]

Fig.6. (b) Adder 9B[19][33].

From the above figures (Fig 34a and 34b), we can see that a Static Energy Recovery XNOR gate is cascaded with the new G-XNOR gate to generate the Sum while the Cout function is implemented by simply multiplexing B and Cin controlled by (A XNOR B) as done in the previous circuits. These two new adders consistently consume less power in high frequencies and have higher speed compared with the previous 10-transistor full adders and the conventional 28-transistor CMOS adder [19][33].

#### G. 12T FULL ADDER:

An energy efficient single bit full adders with 12 transistors using three transistor XOR gate [35], inverters and multiplexer blocks.

Fig.7. Full adder with 12- transistors[19][35]

ICTM Value: 3.00

## SIMULATION RESULTS

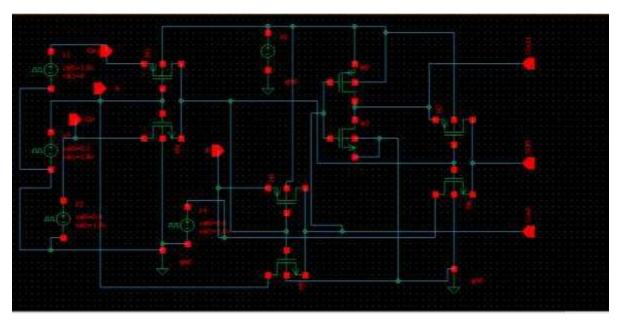

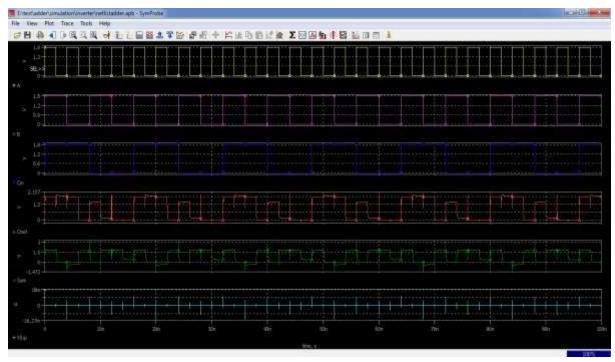

This section summarizes the simulation results. The simulations have been carried out on Symica Electronic Design Automation toolkit. This section comprises of wei et al 2011, 8-T adder cell, proposed 8-T full adder schematic designed in Symica Schematic Editor and rest of the figures are symica symprobe tool generated waveforms for various voltages and current. Although from the output waveforms, it is evident that power in an individual transistor is fluctuating, only average value of this power has been measured and calculated from the reading based on the output waveforms in symica symprobe tool.

Compared to the power consumption of 3.505  $\mu W$  by wei et al 2011, 8-T adder cell, proposed 8-T full adder has a power consumption of only 0.404  $\mu W$ .

The worst case delay of wei et al 2011, 8-T adder cell, proposed 8-T full adder full adder cell have been given in Table 5, calculated from the reading based on the output waveforms in symica symprobe tool, the worst case delay are measured to reach 90% of the steady state value. The total propagation delay is measured as:

$$\tau_P = \frac{\tau_{hl} + \tau_{lh}}{2} \tag{3}$$

ISSN: 2277-9655

**Impact Factor: 4.116**

#### CELL SCHEMATIC AND TRANSIENT RESPONSE OF PREVIOUS WORK

Fig. 8. Wei et al 2011 8-T full adder cell schematic in Symica DE software

ICTM Value: 3.00

ISSN: 2277-9655

**Impact Factor: 4.116**

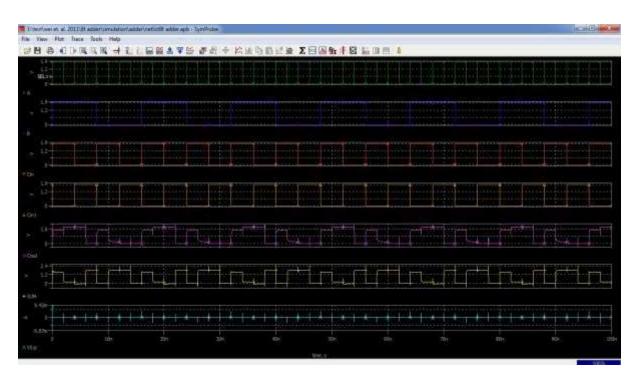

Fig. 9. Output waveforms of wei et. al. 2011 8-T adder in Symprobe software

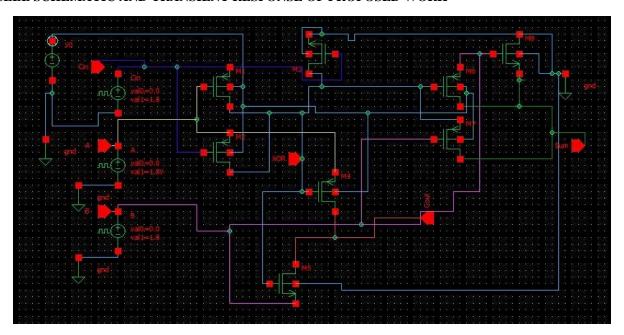

## CELL SCHEMATIC AND TRANSIENT RESPONSE OF PROPOSED WORK

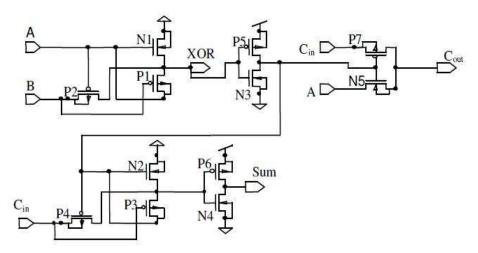

Fig. 10. Proposed 8-T CMOS full adder cell shematic

ISSN: 2277-9655 ICTM Value: 3.00 **Impact Factor: 4.116**

Fig. 11. Simulation output waveforms in Symprobe software

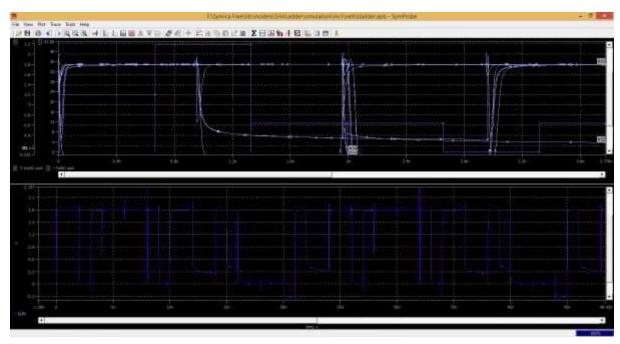

## EYE DIAGRAM OF PROPOSED 8-T FULL ADDER CELL

Fig. 12. Eye diagram of proposed 8-T adder in Symprobe software

ICTM Value: 3.00 **Impact Factor: 4.116**

ISSN: 2277-9655

The worst case delay for wei et al 2011, 8-T adder cell, proposed 8-T full adder cell have been given in Table 5. Compared to the propagation delay of 134.6 ps in wei et al 2011, 8-T adder cell, the proposed 8-T adder cell has a propagation delay of 119.5 ps.

#### **CONCLUSION**

This research work is an attempt to design a full adder Custom Cell Design using 8 transistors in 0.18 µm CMOS Technology. It involves use of 3-T XOR gate to implement the SUM circuit and Cout is implemented using a CMOS Multiplexer and suitable CMOS logic.

Total Power dissipation through wei et al 2011, 8-T adder cell and proposed 8-T full adder have been measured in the symica symprobe tool. A power dissipation of 3.505 µW and 0.404 µW have been obtained through wei et al 2011, 8-T adder cell, proposed 8-T full adder respectively. The best result has been obtained with the proposed adder cell. While comparing to the wei et al 2011, 8-T adder cell, proposed 8-T full addergives an advantage in terms of area, power, delay and power delay product.

This work analyzes the latest developments in low power circuit techniques and methods with an emphasis on speed improvement. Appropriate methods for transistor reduction are studied such as GDI(Gate Diffused Input), Pass transistor logic,etc[44][54]. The proposed work puts forth an8 transistor logic which is a modification over previous work proposed by wei et. al. 2011.

There is substantial reduction in transistor count as this full adder cell using only 8 transistors can be implemented as opposed to conventional 28-T standard CMOS technique.

Power dissipation of 0.404 µw and 3.505 µw have been obtained through Proposed 8-T adder cell and wei et al 2011, 8-T adder cell respectively. Proposed 8-T cell shows the best result in terms of power dissipation and area covered. The worst case propagation delay for proposed cell is 119.5x10-12 seconds and 134.6x10-12 seconds for wei et al 2011, 8-T adder cell.

The proposed work leaves a scope for future improvements related to sizing and area optimization of transistors used in Adder cell so that the power constraint could be taken care of and a smart layout can be prepare to optimize this result further.

#### REFERENCES

- 1. Raju Gupta, Satya Prakash Pandey, Shyam Akashe and Abhay Vidyarthi, 2013 "Analysis and optimization of Active Power and Delay of 10T Full Adder using Power Gating Technique at 45 nm Technology", OSR Journal of VLSI and Signal Processing (IOSR-JVSP), Volume 2, PP 51-57.

- 2. Aminul Islam, M. W. Akram and Mohd.Hasan, 2011, "Energy Efficient and Process Tolerant Full Adder in Technologies beyond CMOS", ACEEE Int. J. on Communication, Vol. 02, No. 02.

- 3. Karthik Reddy. G, 2013, "Low Power-Area Designs of 1bit Full Adder in Cadence Virtuoso Platform", International Journal of VLSI design & Communication Systems (VLSICS), Vol.4, No.4.

- KeivanNavi, MehrdadMaeen, VahidForoutan, SomayehTimarchi and OmidKayehi, 2009, "A novel low-power full-adder cell for low voltage", Integration the VLSI Journal, Volume 42, Issue 4, Pages 457-467.

- 5. Yingtao Jiang, Abdulkarim Al-Sheraidah, Yuke Wang, Edwin Sha and Jin-Gyun Chung 2004, "A novel multiplexer-based low-power full adder", IEEE TRANSACTIOJNS ON CIRCUITS AND SYSTEMS-II: EXPRESS BRIEF, vol. 51, No. 7.

- 6. Hajar Zare Bahramabadi, Hamidreza Dalili Oskouei and Asghar E brahimi, 2013, "Design Low Power Full-Adders for Arithmetic Applications", International Journal of Emerging Science and Engineering (IJESE) ISSN: 2319–6378, Volume-1, Issue-12.

- 7. M. Riyaz Pasha, M. Vinay Kumar and K. Paramesh, 2014, "Design & Implementation Of Low Power Full Adder Cell Using Power Gating Techniques For Mobile Applications", International Journal of Advanced Research in Electronics and Communication Engineering (IJARECE) Volume 3, Issue 8.

[Kumar\**et al.*, 5(8): August, 2016] ISSN: 2277-9655 IC<sup>TM</sup> Value: 3.00 Impact Factor: 4.116

**8.** Janagam. Srinivasa Rao and Gulivindala. Suresh,2013, "Performance Analysis of Full Adder & It's Impact on Multiplier Design", International Journal of Soft Computing and Engineering (IJSCE) ISSN: 2231-2307, Volume-3, Issue-4.

- **9. SantanuMaity, Bishnu Prasad De and Aditya Kr. Singh,**2012, "Design and Implementation of Low-Power High-Performance Carry Skip Adder", International Journal of Engineering and Advanced Technology (IJEAT) ISSN: 2249 8958, Volume-1, Issue-4.

- **10.** BaminGambo, LodTapin ands arat Chandra Hanjabam, 2014, "Low Power and High Performance Full Adder in Deep Submicron Technology", Journal of Electronics and Communication Engineering Research Vol. 2, Issue 3 pp: 07-16 ISSN(Online): 2321-5941.

- **11. Vishal D. Jaiswal, Saroj V. Bakale andSonal S. Bhopale,** 2012, "Implementation And Comparatively Analysis Of Low Power Adder Circuit", International Journal of Advanced Technology & Engineering Research (IJATER) Vol. 2, Issue 2pp: 07-16 ISSN(Online): 2321-5941.

- **12. Namrata Gupta,** 2013, "Designing of Full Adder Circuits for Low Power", International Journal of Scientific Research Engineering & Technology (IJSRET), Volume 2,Issue4,pp 215-219.

- 13. B. Dilip, P. Surya Prasad and R. S. G. Bhavani, 2012, "leakage power reduction in cmos circuits using leakage control transistor technique in nanoscale technology", International Journal of Electronics Signals and Systems (IJESS) ISSN: 2231-5969, Vol-2 Iss-1.

- **14. Dhananjay E. Upasani, Sandip B. Shrote and Pallavi S. Deshpande,** 2010, "Standby Leakage Reduction in Nanoscale CMOS VLSICircuits", international Journal of Computer Applications (0975–8887) Volume 7-No:5.

- **15.** Shubhajit Roy Chowdhury, Aritra Banerjee, Aniruddha Roy and Hiranmay Saha, 2008, "A high Speed 8 Transistor Full Adder Designusing Novel 3 Transistor XOR Gates", World Academy of Science, Engineering and TechnologyInternational Journal of Electrical, Computer, Energetic, Electronic and Communication Engineering Vol:2, No:10.

- **16. M. Geetha Priya and K. Baskaran,** 2013, "Low Power Full Adder With Reduced Transistor Count", International Journal of Engineering Trends and Technology (IJETT) Volume 4 Issue 5.

- **17. Deepa Sinha, Tripti Sharma, K. G. Sharma and Prof. B. P. Singh,** 2011, "*Ultra Low Power 1-Bit Full Adder*", International Symposium on Devices MEMS, Intelligent Systems & Communication (ISDMISC) 2011 Proceedings published by International Journal of Computer Applications (IJCA).

- **18.** Amin Bazzazi, Alireza Mahini and Jelveh Jelini, 2012, "Low Power Full Adder With Reduced Transistor Count", Proceedings of the International MultiConference of Engineers and Computer Scientists IMECS 2012, Vol. II, Hong kong, ISBN: 978-988-19251-9-0, ISSN: 2078-0958 (print); ISSN: 2078-0966 (online).

- **19. Saradindu Panda, A. Baneerjee, B. Maji and Dr. A. K. Mukhopadhyay,** 2012, "Power and Delay Comparison in between different types of Full Adder Circuits", International Journal of Advanced Research in Electrical, Electronics and instrumentation Engineering, Vol. 1, Isue 3, September 2012.

- **20. Yi Wei and Ji-zhong Shen,** 2011, "Design of a novel low power adder \*- transistor 1-bit full adder cell", Journal of Zhejiang University-Science C( Computers and Electronics) ISSN 1869-1951(Print); ISSN 1869:196X(Online) 2011-12(7): 604-607.

- 21. A. Chandrakasan, R. Brodersen, 1995, "Low Power Design", Kluwer Academic Publishers.

- **22. A. M. Shams, and M. A. Bayoumi,** 2000, "A Novel High Performance CMOS 1-bit full Adder Cell", IEEE transactions on circuit and systems, vol. 47, No. 5, May, 2000.

- **23. J. H. Kang and J. B. Kim**, 2004, "design of a low power adder Using Low-Swing Technique", ICSE2004 Proc. 2004, kuala Lumpur, Malaysia.

- **24. A. A. khatibzadeh and K. raahemifar,** 2004, "A study and comparison of Full Adder Cells based on the Standard Static CMOS Logic", IEEE CCECE 2004-CCGEI 2004, Niagara Falls, May 2004.

- **25. S. M. Kang and Y. Leblebici,** 2003, "CMOS Digital Integrated Circuits: Analysis and Design", Third Edition, Tata McGraw-Hill Edition 2003, pp307-316..

- **26. A. Morgenshtein, A. Fish and A. Wagner,**2002, "Gate-Diffused input (GDI): A Power-Efficient Method for Digital Combinational Circuits", IEEE Trans. VLSI Syst., pp 566-581, Oct. 2002..

- 27. I. Hassoune, D. Flandre, I. O'Connor, 2008, "ULPFA: a new efficient design of a power aware full adder", IEEE Transactions on Circuits and Systems I-5438...

[Kumar\**et al.*, 5(8): August, 2016] ICTM Value: 3.00

- **28. R. Zimmermann and \*W. Fichter**, 1997, "Low-power logic styles: CMOS versus pass-transistor logic."IEEE J. Solid-State Circuits, Vol. 32, July 1997, pp 1079-90.

- 29. N. Weste and K. Eshraghian, 1992, "Principles of VLSI design, A system perspective", Reading, M. A: Addision Wesley, 1993.

ISSN: 2277-9655

**Impact Factor: 4.116**

- 30. N. Zhuang and H. Wu, 1993, "New design of the CMOS Full Adder", IEEE J. Solid-State Circuits, Vol. 27, no. 5, pp 840-844, May 1992.

- 31. J. Wang, S. Fang and W. Feng, 1994, "New efficient designs for XOR and XNOR functions on the

- transistor level", IEEE J. Solid-State Circuits, vol. 29, no.7, Jul. 1994, pp. 780-786.

32. AR. Shalem, E. John, and L. K. John, 1999, "A Novel Low Power Energy recovery Full Adder Cell", in Proc. IEEE Great Lakes VLSI Symp., pp 380-383, feb 1999.

- 33. H. T. Bui, A. K. Al-Sheraidah and Y. wang, 2000, "Design and Analysis of 10-transistor Full Adders using Novel XOR-XNOR Gates", Proceedings of ICSP2000.

- 34. P. M. Lec, C. H. Hsu, and Y. H. Hung, 2007, "Novel 10-T full adders realized by GDI structure", IEEE International Symposium on Integrated Circuits(ISIC-2007).

- 35. J. F. Lin, Y. T. Hwang, M. H. Sheu and C. C. Ho, 2007, "A Novel High Speed and Energy efficient 10-Transistor Full Adder Design", IEEE Transactions on Circuits and System-1 Regular Papers, vol. 54, no. 5, May 2007.

- **36. D. Radhakrishnan,** 2001, "Low-voltage low-power CMOS full adder", in Proc. IEEE Circuits Devices Systems, Vo. 148, Feb 2001, pp 19-24.

- 37. S. Goel, A. Kumar, M. A. Bayoumi, 2006, "Design of Robust, Energy-Efficient Full Adders for Deep-Submicrometer Design Using Hybrid-CMOS Logic", IEEE Transactions on VLSI 2006.

- 38. N. F. goncalves and H. J. De Man, 1983, "NORA: A race-free dynamic CMOS technologyfor pipelined logic structures," IEEE J. Solid-State Circuits, vol. SSC-18, no. 6, pp. 261-266, June 1983.

- 39. M. S. Elrabaa, I. S. Abu-Khater, and M. I. Elmasry, 1997, "Advanced Low-Power Digital Circuit Techniques" Boston: Kluwer Academic Publishers.

- 40. F.A. Najm, 1993, "Transition Density: A New Measure of Activity in Digital Circuits," IEEE Transactions on Computer Aided Design, vol. 12, no. 2, pp. 310-323, feb. 1993.

- 41. J. M. Rabaey and M. Pedram, editors, 1996, "Low Power Design Methodologies" Boston: Kluwer Academic Publishers.

- 42. SiriUppalapati, 2004, "Low Power Design of Standard Cell Digital VLSI Circuits" M. Sc. Thesis, New Brunswick, New Jersey, Oct. 2004.

- 43. K. Roy, S. Mukhopadhyay and H. Mahmoodi-Meimand, 2003, "Leakage current mechanisms and leakage reduction techniques in deep-submicrometer CMOS circuits" in *Proceedings of the IEEE*, vol. 91, no. 2, pp. 305-327, Feb 2003.

- 44.P. F. Butzen and R. P. Ribas, 2005. "Leakage Current in Sub-Micrometer CMOS Gates," University of Federal do Rio Grande do SuI.

- 45. Gronowski, P. E. et al., 1998, "High-Performance Microprocessor Design", IEEE Journal of Solid State Circuits, New York, v.33, n.5, p. 676-686, May 1998.

- 46. Takayanagi, T. et al., 2005, "A Dual-Core 64-bit UltraSPARC Microprocessor for Dense Server Applications", IEEE Journal of Solid State Circuits, New York, v.40, n.1, p. 7-17, Jan. 2005.

- 47. Leon, A. S. et al., 2007, "A Power-Efficient High-Throughput 32-Thread SPARC Processor". IEEE Journal of Solid State Circuits, New York, v.42, n.1, p. 7-16, Jan 2007.

- 48. VEENDRICK, H.J.M., 1984, "Short-Circuit Dissipation of Static CMOS Circuitry and its Impact on the Design of Buffer Circuits", IEEE Journal of Solid State Circuits, New York, v.SC-19, n.4, p. 468-473, Aug.

- **49. SOUDRIS, D. et al.,** 2002, "Designing CMOS circuits for low power", Boston: Kluwer Academic, 2002.

- 50. MOORE, G. E., 2003, "No exponential is forever: but 'Forever' can be delayed!", In IEEE INT. CONF. SOLID STATE CIRCUITS, 2003. Proceedings of IEEE, pp. 20-23.

- 51. ROY, K. et al., 2003, "Leakage Current Mechanisms and Leakage Reduction Techniques in Deep-Submicrometer CMOS Circuits", Proceedings of IEEE, New York, v.91, n.2, p. 305-327, Feb 2003.

- 52. AGARWAL, A. et al., 2005, "Leakage Power Analysis and Reduction: Models, Estimation and Tools", Proc. IEE, v.152, n.3, p 353-368, May 2005.

- 53. Nan Zhuang, Haomin Wu, 1992, "A new design of the CMOS Full Adder", IEEE Journal of Solid-State Circuits, Vol. 27, No. 5, May 1992. **54. Rohit Tripathi,** 2015," To design a low power full adder cell with minimum power and delay" M. Tech.

- Thesis, G. B. Pant University, Pantnagar, Uttarakhand, June 2015.

- **55. Symica Design Environment quick start,** Symica LLC 2009-2013, www.symica.com.